**Double Edge Triggered Flip Flop Designing Using Various**

# Mos Logic Techniques

M. Sundararajan\*, B. Karthik, M. Susila,

Dept of ECE, Bharath University, Chennai,

\*Corresponding author: E-Mail:msrajan69@gmail.com

# ABSTRACT

This novel depends on the configuration of high execution and force productive circuits to lessen the force utilization of Flip Flop what's more, locks. The different force effective flip-lemon with the low power clock dissemination system are inspected. In these flips- flounders the Low Power Clocked Pass Transistor Flip-Flop – in short LCPTFF devours slightest force than Double Edge Triggered Flip Flop - DETFF, Clocked Pair Shared Flip-Flop(CPSFF), Conditional Data Mapping Flip-Flop (CDMFF) what's more, Conditional Discharge Flip Flop - CDFF.A novel in view of the usage of Low Power Multi Threshold Corresponding Metal Oxide Semiconductor Timed Pass Transistor Flip-Flop LP- MTCPTFF to accomplish force diminishment and additionally the transistor can be lessened by contrasting those above systems.

# KEYWORDS: Edge, Flip Flop, DETFF, MTCPTFF.

# **1. INTRODUCTION**

The System of Chip (SOC) plan incorporates a huge number of transistors on a solitary chip as a result there is a lot of force scattering occurring in the circuit. The VLSI creators were more disposed towards diminishing the zone and improving the computational rate of the circuits, though the force utilization was a vital element. Late years, have demonstrated that power utilization is similarly imperative in examination to territory and velocity to high execution circuit. With perpetually expanding interest of handheld convenient gadgets, Individual Digital Assistance and Personal Specialized Devices, lessening the on- chip power utilization assumes a key part in expanding the battery life.

**Force Consumption:** Force utilizations are basic at the chip level on the grounds that a significant part of the force is disseminated as warmth, and chips have constrained warmth dispersal limit. Regardless of the fact that the framework in which a chip is set can supply a lot of force, most chips are bundled to disperse less than 10 to 15 watts of force before they endure changeless harm. The force utilization of a rationale circuit is restricted by putting the number of transistors on a solitary chip. Restricting the quantity of transistors per chip changes framework plan in a few ways. Required to send the same sign between two transistors on the same chip. Thus, some of the upside of utilizing a higher-pace circuit family is lost. Another inconspicuous impact of diminishing the level of incorporation is that the electrical configuration of multi-chip frameworks is more intricate, minuscule wires on-chip show parasitic resistance and capacitance, while plainly visible wires between chips have capacitance and inductance, which can bring about a number of ringing impacts that are much harder to break down.

# Low Power Techniques

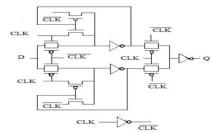

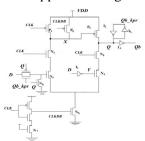

**Double Edge Triggered Flip Flop:** The (DEFF)- Double Edge Flip Flop as appeared in fig.1 utilize more Timed Transistors than (SEFF)-Single Edge Flip Flop. Then again, DEFF configuration ought won't build the clock stack as well as much. The (DEFF) configuration ought to go for sparing vitality together on the circulation system by halfing the recurrence and also flip-lemon. This is desirable over diminish Circuits Clock Loads by reducing the quantity of (TT) Timed Transistors. These circuits with lessened exchanging movement will be best. Low Swing capacity is extremely supportive to additional decrease the voltage on the (CC) Clock Conveyance system for force sparing. Because of the way that voltage scaling can lessen power productively. Clock branch sharing topology is utilized as a part of this strategy.

**Force Dissipation of a DETFF:** Inner power scattering Power devoured by the inward and information hubs amid hooking operations, including the force disseminated driving the yield load. Neighborhood clock power dispersal Portion of the force scattered in the clock cushion that is driving the clock data of the flip-failure. Neighborhood information power dispersal the part of the force scattered in the rationale entryway that is driving the information data of the flip-lemon. The clock power scattering is dictated by the clock heap of the flip failure, while the appropriation of the inner and information power dissemination is influenced by the structure and operation of the locking component itself and the data exchanging movement.

Each of the three parts of force require autonomous estimation in any relative investigation in light of the fact that, innately, a trade off exists between the three. On the off chance that an examination is made without taking every one of the three segments into record, it might show deluding results. The timing portrayal contains two deferral parameters. The main deferral is the time measurement is done between the Clock Edge and the Yield Edge. Then the second defer is the time measured between the Info Information Edge and the Yield edge. The recent variable is regularly alluded to as idleness of a flip-lemon.

## www.jchps.com

# Journal of Chemical and Pharmaceutical Sciences

One compares to rising edge of the clock and the other compares to the Falling edge of the clock. These two attributes are autonomous of one another what's more, for the most part are not the same? A trade off in the middle of velocity and force utilization is regularly conceivable, and it is regularly dictated by the application. Subsequently, a given flip-failure can either be improved for elite or low power. Then again, when both force dissemination and execution are basic, one needs to decide a configuration that works at the ideal.

#### Figure.1. The two attributes are gotten.

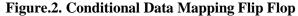

**Conditional Discharge Flip Flop:** The Conditional Discharge Flip Flop not just decreases the interior exchanging exercises, additionally creates less glitch at the yield, while looking after the negative setup time and little info to yield postponement. The restrictive release innovation is utilized as a part of this method.

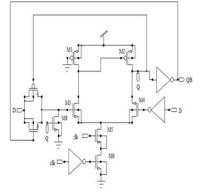

As appeared in fig.2 CDFF works for both understood and additionally unequivocal heartbeat activated flipfailure frameworks. In CDFF an uncommon Pulse generator circuit is utilized which creates clock beat that help us to trigger the circuit at both positive and the negative edges thus the entire framework takes a shot at twofold edge activated innovation as appeared in fig 3.

In CDFF the excess exchanging action is minimized by controlling the release way by utilizing a nMOS transistor at the base which is driven by information Qb. The CDFF works in two modes first is the low to high move when information is high, and the second is the high to low move when data turns out to be low. The CDFF decreases the force dissemination by fusing twofold edge activated technology. However, the primary disservice of this circuit is that zone is expanded by utilizing an express heartbeat generator circuit.

#### Figure.3. pulse generator circuit

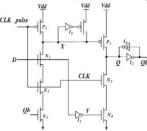

**Conditional Data Mapping Flip Flop:** In the flip-failures when the inputs are (0, 0) memory state is held that is Q and Qb holds their present qualities. The CDMFF adventures the property of the flip-failures by mapping the inputs back to (0, 0) when any sort of repetitive exchanging occasion is anticipated by utilizing Q and Qb as the control signals. All this is set up with the assistance of an information mapping circuit. The restrictive information mapping innovation is utilized as a part of this procedure as appeared in fig 4.

#### Figure.4. Conditional Data Mapping Flip Flop

S - 261

#### ISSN: 0974-2115

# www.jchps.com

# Journal of Chemical and Pharmaceutical Sciences

The repetitive checking capacitance in CDMFF remains information 0 or 1, for pre-charging transistors (P1 and P2), keep exchanging without valuable calculation, bringing about repetitive timing. It is important to diminish repetitive force utilization here. CDMFF has a drifting hub on basic way since the initial stage is alterable. Whenever clock sign CLK travels from zero to1, pulse generator (CLKDB) will stay 1 for a brief period that creates an certain heartbeat window for the assessment. Amid that P1, P2 are in OFF. In the event that D travels (from 0 to 1), the draw downwards system will be separated by N3 utilizing information map plan. In the event that D is 0, the draw down system is separated from GND as well. Thus interior hub X is not associated with  $V_{dd}$  or GND amid maximum heartbeat.

The significant point of interest of CDMFF is that decreases the check in examination with CDFF thus there is a diminishment in the force dispersal in CDMFF. The D to Q postponement of CDMFF is better when contrasted with CDFF

On the off chance that a clamor releases the hub X, P-MOS transistor P3 may be incompletely on, and a glitch will show up on yield hub Q. In a nano scale circuit, a glitch expends force as well as could engender to the following stage which makes the framework more powerless against commotion. Subsequently, CDMFF couldn't be utilized as a part of clamor serious environment. This is hard for applying the low power procedures presented the pulse structure with pre-charging transistors in (CDMFF) makes it hard to apply twofold edge activating. CDMFF be utilized as a part of a Low Swing Clock (LSC) environment. The approaching low swing clock sign can't drive pMOS, P1 and P2, in high voltage square , in light of the fact that the pMOS transistors won't kill by a low swing voltage (LSV), bringing about short out force utilization.

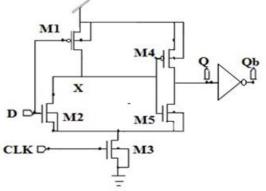

# Figure.5. Clocked Pair Share FlipFlop Figure.6. Clocked Pass Transistor Flip Flop MTCMOS Technique: For effective force administration in MTCMOS innovation, the circuit takes a shot at two modes, one being the "dynamic" and the other "rest" operational modes. The routine circuit takes a shot at single limit voltage (Vt) while the circuit utilizing the MTCMOS procedure takes a shot at two distinctive edge voltage switches are Low Vt and High Vt. The circuit involves two distinctive arrangement of transistors- one which takes a shot at High Vt are termed as "rest" transistors and the transistors which takes a shot at Low Vt involves the sensible circuit.

The rest transistors are utilized to accomplish high execution by diminishing the spillage current while the Low Vt transistors upgrade the circuit's rate execution. The fig.7 comprises of two rest transistors S1 and S2 with higher Vt. The rationale circuit between the S1 and S2 is not specifically associated with genuine supply lines Vdd what's more, Gnd, yet thus it is joined with virtual power supply lines Vddv and Gndv and has low Vt. The above mentioned circuit works in both dynamic mode and standby mode. In dynamic mode, S=0, SBAR=1 such that S1 and S2 are in ON and virtual supply lines (Vddv and Gndv ) work as genuine supply lines in this way the rationale circuit works typically and at a higher rate. In rest mode, S=1 and SBAR=0 such that S1 What's more, S2 are OFF and this will bring about virtual power supply line to buoy and substantial (SC) Spillage Current present in circuit is smothered by rest transistors S1 and S2 bringing about low spillage current and along these lines diminishing force utilization.

# 2. CONCLUSION AND FUTUREWORK

The downside of the timed pair shared flip failure method is the prerequisite of the transistor gets expanded by contrasting with the low power timed pass transistor rationale. Henceforth by diminishing the general transistor the aggregate force utilization get decreased. By actualizing the MTCMOS method the aggregate force dispersal get diminished. The another fundamental inconvenience of Clocked Pair Shared Flip Flop procedure is that give commotion coupling at higher frequencies

The proposed novel is to execute this MTCMOS innovation for Low Power Timed Pass Transistor Flip Flop. This technique is productive by lessening the aggregate transistors utilizing LP-CPTFF and MTCMOS procedure is

# www.jchps.com

# Journal of Chemical and Pharmaceutical Sciences

utilized to diminish the short out force dispersal. This novel can be executed in 40nm innovation utilizing Tanner EDA devices.

# REFERENCES

Bhuvana S, Sangeetha R, A Survey on Sequential Elements for Low Power Clocking System, Journal of Computer Applications, 5(3), 2012.

Gopalakrishnan K, Sundar Raj M, Saravanan T, Multilevel inverter topologies for high-power applications, Middle - East Journal of Scientific Research, 20(12), 2014, 1950-1956.

Hemantha S, Dhawan, An and Kar.H,Multi-edge CMOS outline for low power advanced circuits, TENCON 2008-2008 IEEE Region 10 Conference, 2008, 1-5.

Jasmin M, Vigneshwaran T, Beulah Hemalatha S, Design of power aware on chip embedded memory based FSM encoding in FPGA, International Journal of Applied Engineering Research, 10(2), 2015, 4487-4496.

Kang S.M, Leblebici Y, CMOS Digital Integrated Circuits investigation and configuration, third release, TMH, 2003.

Kanniga E, Selvaramarathnam K, Sundararajan M, Kandigital bike operating system, Middle - East Journal of Scientific Research, 20(6), 2014, 685-688.

Kanniga E, Sundararajan M, Modelling and characterization of DCO using pass transistors, Lecture Notes in Electrical Engineering, 86(1), 2011, 451-457.

Karthik B, Arulselvi, Noise removal using mixtures of projected gaussian scale mixtures, Middle - East Journal of Scientific Research, 20(12), 2014, 2335-2340.

Karthik B, Arulselvi, Selvaraj A, Test data compression architecture for lowpower vlsi testing, Middle - East Journal of Scientific Research, 20(12), 2014, 2331-2334.

Karthik B, Kiran Kumar T.V.U, Authentication verification and remote digital signing based on embedded arm (LPC2378) platform, Middle - East Journal of Scientific Research, 20(12), 2014, 2341-2345.

Karthik B, Kiran Kumar T.V.U, EMI developed test methodologies for short duration noises, Indian Journal of Science and Technology, 6(5), 2013, 4615-4619, 2013.

Karthik B, Kiran Kumar T.V.U, Vijayaragavan P, Bharath Kumaran E, Design of a digital PLL using 0.35Î<sup>1</sup>/4m CMOS technology, Middle - East Journal of Scientific Research, 18(12), 2013, 1803-1806.

Philomina S, Karthik B, Wi-Fi energy meter implementation using embedded linux in ARM 9, Middle - East Journal of Scientific Research, 20(12), 2014, 2434-2438.

Saravanan T, Sundar Raj M, Gopalakrishnan K, Comparative performance evaluation of some fuzzy and classical edge operators, Middle - East Journal of Scientific Research, 20(12), 2014, 2633-2633.

Saravanan T, Sundar Raj M, Gopalakrishnan K, SMES technology, SMES and facts system, applications, advantages and technical limitations, Middle - East Journal of Scientific Research, 20(11), 2014, 1353-1358.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, A DFIG based wind generation system with unbalanced stator and grid condition, Middle - East Journal of Scientific Research, 20(8), 2014, 913-917.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Effective routing technique based on decision logic for open faults in fpgas interconnects, Middle - East Journal of Scientific Research, 20(7), 2014, 808-811.

Vijayaragavan S.P, Karthik B, Kiran Kumar T.V.U, Privacy conscious screening framework for frequently moving objects, Middle - East Journal of Scientific Research, 20(8), 2014, 1000-1005.